#### Xilinx ISE Design Suite 10.1 Software Manuals

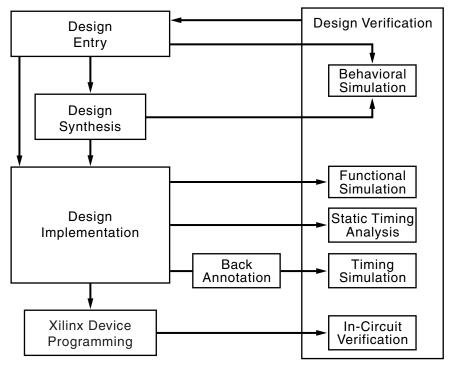

These software manuals support the Xilinx<sup>®</sup> Integrated Software Environment (ISE<sup>TM</sup>) software. Click a manual title on the left to view a manual, or click a design step in the following figure to list the manuals associated with that step.

**Note:** To get started with the software, refer to the "Getting Started Manuals." For information on graphical user interfaces (GUIs), see the Help provided with each GUI.

# **Getting Started Manuals**

| Title                        | Summary                                                                                                                                                                                                                                                                                |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ISE Quick Start Tutorial     | <ul> <li>Explains how to use VHDL and verilog design entry tools</li> <li>Explains how to perform functional and timing simulation</li> <li>Explains how to implement a sample design</li> </ul>                                                                                       |

| EDK Supplemental Information | <ul> <li>Describes how to get started with the Embedded Development Kit (EDK)</li> <li>Includes information on the MicroBlaze<sup>TM</sup> and the IBM<sup>®</sup> PowerPC<sup>®</sup> processors</li> <li>Includes information on core templates and Xilinx device drivers</li> </ul> |

# **Design Entry Manuals**

| Title                                                                                                                                                                      | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ChipScope Documentation  Note: These documents are available on the Web. ChipScope Pro is one of the Optional Design Tools that can be purchased by clicking Online Store. | <ul> <li>Explains how to use the ChipScope™ Pro Core Generator™ tool to generate ChipScope Pro cores and add them to an FPGA design</li> <li>Explains how to use the ChipScope Pro Core Inserter tool to insert cores into a post-synthesis netlist without disturbing the HDL source code</li> <li>Explains how to use the ChipScope Pro Analyzer tool to perform incircuit verification (also known as on-chip debugging), including how to view data and interact with ChipScope Pro cores, how to create bitstreams that are compatible with the ChipScope Pro JTAG download function, and how to download bitstreams to an FPGA using JTAG</li> </ul> |

| Constraints Guide                                                                                                                                                          | <ul> <li>Describes each Xilinx constraint, including supported architectures, applicable elements, propagation rules, and syntax examples</li> <li>Describes constraint types and constraint entry methods</li> <li>Provides strategies for using timing constraints</li> <li>Describes supported third party constraints</li> </ul>                                                                                                                                                                                                                                                                                                                       |

| Data2Mem User Guide                                                                                                                                                        | <ul> <li>Describes how the Data2MEM software tool automates and simplifies setting the contents of BRAM cells on Virtex™ devices.</li> <li>Includes how this is used with the 32-bit CPU on the single-chip Virtex-II Pro devices</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                               |

| EDK Supplemental Information  Note: These documents are available on the Web.                                                                                              | <ul> <li>Describes how to get started with the Embedded Development Kit (EDK)</li> <li>Includes information on the MicroBlaze and the IBM PowerPC processors</li> <li>Includes information on core templates and Xilinx device drivers</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                          |

| Hardware User Guides  Note: These manuals are available on the Web.                                                                                                        | <ul> <li>Describes the function and operation of Virtex-II and Virtex-II Pro devices, including information on the RocketIO™ transceiver and IBM PowerPC processor</li> <li>Describes how to achieve maximum density and performance using the special features of the devices</li> <li>Includes information on FPGA configuration techniques and printed circuit board (PCB) design considerations</li> </ul>                                                                                                                                                                                                                                             |

| ISE Quick Start Tutorial                                                                                                                                                   | <ul> <li>Explains how to use VHDL and verilog design entry tools</li> <li>Explains how to perform functional and timing simulation</li> <li>Explains how to implement a sample design</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Libraries Guide Manuals                                                                                                                                                    | <ul> <li>Includes Xilinx Unified Library information arranged by slice count, supported architectures, and functional categories</li> <li>Describes each Xilinx design element, including architectures, usage information, syntax examples, and related constraints</li> </ul>                                                                                                                                                                                                                                                                                                                                                                            |

| Synthesis and Simulation Design<br>Guide                                                                                                                                   | <ul> <li>Provides a general overview of designing Field Programmable Gate<br/>Arrays (FPGA devices) with Hardware Description Languages (HDLs)</li> <li>Includes design hints for the novice HDL designer, as well as for the<br/>experienced designer who is designing FPGA devices for the first time</li> </ul>                                                                                                                                                                                                                                                                                                                                         |

| Title                               | Summary                                                                                                                                                                                                                                                                           |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Xilinx/Cadence PCB Guide            | <ul> <li>Provides information information for FPGA designers and Printed Circuit Board (PCB )engineers.</li> <li>Includes information about processes and mechanisms available within ISE and various Cadence tools to efficiently implement an FPGA on a PCB.</li> </ul>         |

| Xilinx/Mentor Graphics PCB<br>Guide | <ul> <li>Provides information information for FPGA designers and Printed Circuit Board (PCB )engineers.</li> <li>Includes information about processes and mechanisms available within ISE and various Mentor Graphics tools to efficiently implement an FPGA on a PCB.</li> </ul> |

*Note:* For more information, see the ISE Help provided with the Project Navigator GUI.

# **Design Synthesis Manuals**

| Title                                    | Summary                                                                                                                                                                                                                                                                                                            |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ISE Quick Start Tutorial                 | <ul> <li>Explains how to use VHDL and verilog design entry tools</li> <li>Explains how to perform functional and timing simulation</li> <li>Explains how to implement a sample design</li> </ul>                                                                                                                   |

| Synthesis and Simulation Design<br>Guide | <ul> <li>Provides a general overview of designing Field Programmable Gate<br/>Arrays (FPGA devices) with Hardware Description Languages (HDLs)</li> <li>Includes design hints for the novice HDL designer, as well as for the<br/>experienced designer who is designing FPGA devices for the first time</li> </ul> |

| XST User Guide                           | <ul> <li>Explains how to use Xilinx Synthesis Technology (XST) synthesis tool, and how it supports HDL languages, Xilinx devices, and constraints</li> <li>Explains FPGA and CPLD optimization techniques</li> <li>Describes how to run XST from the Project Navigator Process window and command line</li> </ul>  |

### **Design Implementation Manuals**

| Title                                 | Summary                                                                                                                                                                                                                                                    |

|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Development System<br>Reference Guide | <ul> <li>Describes Xilinx design flows, including hierarchical design flows such as<br/>Incremental Design and Modular Design</li> <li>Describes FPGA and CPLD command line tools, including syntax,<br/>options, input files, and output files</li> </ul> |

|                                       | <b>Note:</b> For information on design implementation, see the "NGDBuild," "MAP," "PAR," and "BitGen" chapters for FPGAs, and see the "NGDBuild," "CPLDFit," and "HPrep6" chapters for CPLDs.                                                              |

**Note:** For information on GUIs, such as the Project Navigator, Constraints Editor, ECS, Floorplanner, FPGA Editor, iMPACT, PACE, Timing Analyzer, and XPower, see the Help provided with each tool.

### **Behavioral Simulation Manuals**

| Title                                    | Summary                                                                                                                                                                                                                                                                                                            |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ISE Quick Start Tutorial                 | <ul> <li>Explains how to use VHDL and verilog design entry tools</li> <li>Explains how to perform functional and timing simulation</li> <li>Explains how to implement a sample design</li> </ul>                                                                                                                   |

| Libraries Guide Manuals                  | <ul> <li>Includes Xilinx Unified Library information arranged by slice count, supported architectures, and functional categories</li> <li>Describes each Xilinx design element, including architectures, usage information, syntax examples, and related constraints</li> </ul>                                    |

| Synthesis and Simulation Design<br>Guide | <ul> <li>Provides a general overview of designing Field Programmable Gate<br/>Arrays (FPGA devices) with Hardware Description Languages (HDLs)</li> <li>Includes design hints for the novice HDL designer, as well as for the<br/>experienced designer who is designing FPGA devices for the first time</li> </ul> |

Note: For more information, see the ISE Help available from the Project Navigator GUI.

### **Functional Simulation Manuals**

| Title                                    | Summary                                                                                                                                                                                                                                                                                                            |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ISE Quick Start Tutorial                 | <ul> <li>Explains how to use VHDL and verilog design entry tools</li> <li>Explains how to perform functional and timing simulation</li> <li>Explains how to implement a sample design</li> </ul>                                                                                                                   |

| Libraries Guide Manuals                  | <ul> <li>Includes Xilinx Unified Library information arranged by slice count, supported architectures, and functional categories</li> <li>Describes each Xilinx design element, including architectures, usage information, syntax examples, and related constraints</li> </ul>                                    |

| Synthesis and Simulation Design<br>Guide | <ul> <li>Provides a general overview of designing Field Programmable Gate<br/>Arrays (FPGA devices) with Hardware Description Languages (HDLs)</li> <li>Includes design hints for the novice HDL designer, as well as for the<br/>experienced designer who is designing FPGA devices for the first time</li> </ul> |

Note: For more information, see the ISE Help available from the Project Navigator GUI.

# **Static Timing Analysis Manuals**

| Title                                 | Summary                                                                                                                                                                                                                                            |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Development System<br>Reference Guide | <ul> <li>Describes Xilinx design flows, including hierarchical design flows such as Incremental Design and Modular Design</li> <li>Describes FPGA and CPLD command line tools, including syntax, options, input files, and output files</li> </ul> |

|                                       | <b>Note:</b> For information on static timing analysis, see the "TRACE" chapter for FPGAs, and see the "TAEngine" chapter for CPLDs. Also, see the "NetGen" chapter.                                                                               |

Note: For more information, see the Help provided with the Timing Analyzer GUI.

### **Timing Simulation and Back Annotation Manuals**

| Title                                 | Summary                                                                                                                                                                                          |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Development System<br>Reference Guide | Describes Xilinx design flows, including hierarchical design flows such as<br>Incremental Design and Modular Design                                                                              |

|                                       | <ul> <li>Describes FPGA and CPLD command line tools, including syntax,<br/>options, input files, and output files</li> </ul>                                                                     |

|                                       | <b>Note:</b> See the "NetGen" chapter for information on timing simulation and back annotation.                                                                                                  |

| ISE Quick Start Tutorial              | <ul> <li>Explains how to use VHDL and verilog design entry tools</li> <li>Explains how to perform functional and timing simulation</li> <li>Explains how to implement a sample design</li> </ul> |

*Note:* For more information, see the ISE Help provided with the Project Navigator GUI.

### **In-Circuit Verification Manuals**

| Title                                                                                                                                                                      | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ChipScope Documentation  Note: These documents are available on the Web. ChipScope Pro is one of the Optional Design Tools that can be purchased by clicking Online Store. | <ul> <li>Explains how to use the ChipScope Pro Core Generator tool to generate ChipScope Pro cores and add them to an FPGA design</li> <li>Explains how to use the ChipScope Pro Core Inserter tool to insert cores into a post-synthesis netlist without disturbing the HDL source code</li> <li>Explains how to use the ChipScope Pro Analyzer tool to perform incircuit verification (also known as on-chip debugging), including how to view data and interact with ChipScope Pro cores, how to create bitstreams that are compatible with the ChipScope Pro JTAG download function, and how to download bitstreams to an FPGA using JTAG</li> </ul> |

| Development System<br>Reference Guide                                                                                                                                      | <ul> <li>Describes Xilinx implementation tools and design flows, including the hierarchical flows such as Incremental Design, Modular Design, and Partial Reconfiguration</li> <li>Includes reference information for Xilinx FPGA and CPLD command line tools, including syntax, input files, output files, and options</li> <li>Note: See the "Design Flow" chapter for information on using "PROBE" in FPGA Editor.</li> </ul>                                                                                                                                                                                                                         |

### **Xilinx Device Programming Manuals**

| Title                                                                 | Summary                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Sheets Note: These documents are available on the Web.           | <ul> <li>Describes the Xilinx device families</li> <li>Provides device ordering information</li> <li>Includes detailed functional descriptions, electrical and performance characteristics, and pinout and package information</li> </ul>                                                                                                                                                                     |

| Hardware User Guides  Note: These documents are available on the Web. | <ul> <li>Describes the function and operation of Virtex-II and Virtex-II Pro devices, including information on the RocketIO transceiver and IBM PowerPC processor</li> <li>Describes how to achieve maximum density and performance using the special features of the devices</li> <li>Includes information on FPGA configuration techniques and printed circuit board (PCB) design considerations</li> </ul> |

*Note:* For more information, see the Online Help provided with the iMPACT GUI.

#### **Libraries Guide Manuals**

| Title                                                                     | Summary                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPLD Libraries Guide                                                      | <ul> <li>Includes Xilinx Unified Library information for CPLD specific devices.</li> <li>Describes each Xilinx design element, including supported CPLD architectures, usage information, syntax examples, and related constraints</li> </ul>                                                                                                                        |

| Spartan-II and Spartan-IIE<br>Libraries Guide for HDL Designs             | <ul> <li>Includes a general description of the Spartan<sup>TM</sup>-II and Spartan-IIE architecture</li> <li>Includes a list of all Spartan-II/IIE design elements that can be instantiated using VHDL or Verilog code organized by functional categories</li> <li>Includes examples of code that can be cut and pasted into a design using a text editor</li> </ul> |

| Spartan-II and Spartan-IIE<br>Libraries Guide for Schematic<br>Designs    | <ul> <li>Includes a general description of the Spartan-II and Spartan-IIE architecture</li> <li>Includes a list of all of the Spartan-II/IIE design elements for which schematic symbols are available, organized by their respective functional categories</li> </ul>                                                                                               |

| Spartan-3 Libraries Guide for HDL Designs                                 | <ul> <li>Includes a general description of the Spartan-3 architecture</li> <li>Includes a list of all Spartan-3 design elements that can be instantiated using VHDL or Verilog code organized by functional categories</li> <li>Includes examples of code that can be cut and pasted into a design using a text editor</li> </ul>                                    |

| Spartan-3 Libraries Guide for<br>Schematic Designs                        | <ul> <li>Includes a general description of the Spartan-3 architecture</li> <li>Includes a list of all of the Spartan-3 design elements for which schematic symbols are available, organized by their respective functional categories</li> </ul>                                                                                                                     |

| Spartan-3A and Spartan-3A DSP<br>Libraries Guide for HDL Designs          | <ul> <li>Includes a general description of the Spartan-3A architecture</li> <li>Includes a list of all Spartan-3A design elements that can be instantiated using VHDL or Verilog code organized by functional categories</li> <li>Includes examples of code that can be cut and pasted into a design using a text editor</li> </ul>                                  |

| Spartan-3A and Spartan-3A DSP<br>Libraries Guide for Schematic<br>Designs | <ul> <li>Includes a general description of the Spartan-3A architecture</li> <li>Includes a list of all of the Spartan-3A design elements for which schematic symbols are available, organized by their respective functional categories</li> </ul>                                                                                                                   |

| Spartan-3E Libraries Guide for<br>HDL Designs                             | <ul> <li>Includes a general description of the Spartan-3E architecture</li> <li>Includes a list of all Spartan-3E design elements that can be instantiated using VHDL or Verilog code organized by functional categories</li> <li>Includes examples of code that can be cut and pasted into a design using a text editor</li> </ul>                                  |

| Title                                                        | Summary                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Spartan-3E Libraries Guide for<br>Schematic Designs          | <ul> <li>Includes a general description of the Spartan-3E architecture</li> <li>Includes a list of all of the Spartan-3E design elements for which schematic symbols are available, organized by their respective functional categories</li> </ul>                                                                                                     |

| Virtex and Virtex-E Libraries<br>Guide for HDL Designs       | <ul> <li>Includes a general description of the Virtex and Virtex-E architectures</li> <li>Includes a list of all Virtex and Virtex-E design elements that can be instantiated using VHDL or Verilog code organized by functional categories</li> <li>Includes examples of code that can be cut and pasted into a design using a text editor</li> </ul> |

| Virtex and Virtex-E Libraries<br>Guide for Schematic Designs | <ul> <li>Includes a general description of the Virtex and Virtex-E architectures</li> <li>Includes a list of all of the Virtex and Virtex-E design elements for which schematic symbols are available, organized by their respective functional categories</li> </ul>                                                                                  |

| Virtex-II Libraries Guide for HDL<br>Designs                 | <ul> <li>Includes a general description of the Virtex-II architectures</li> <li>Includes a list of all Virtex-II design elements that can be instantiated using VHDL or Verilog code organized by functional categories</li> <li>Includes examples of code that can be cut and pasted into a design using a text editor</li> </ul>                     |

| Virtex-II Libraries Guide for<br>Schematic Designs           | <ul> <li>Includes a general description of the Virtex-II architectures</li> <li>Includes a list of all of the Virtex-II design elements for which schematic symbols are available, organized by their respective functional categories</li> </ul>                                                                                                      |

| Virtex-II Pro Libraries Guide for<br>HDL Designs             | <ul> <li>Includes a general description of the Virtex-II Pro architectures</li> <li>Includes a list of all Virtex-II Pro design elements that can be instantiated using VHDL or Verilog code organized by functional categories</li> <li>Includes examples of code that can be cut and pasted into a design using a text editor</li> </ul>             |

| Virtex-II Pro Libraries Guide for<br>Schematic Designs       | <ul> <li>Includes a general description of the Virtex-II Pro architectures</li> <li>Includes a list of all of the Virtex-II Pro design elements for which schematic symbols are available, organized by their respective functional categories</li> </ul>                                                                                              |

| Virtex-4 Libraries Guide for HDL<br>Designs                  | <ul> <li>Includes a general description of the Virtex-4 LX/SX/FX architectures</li> <li>Includes a list of all Virtex-4 design elements that can be instantiated using VHDL or Verilog code organized by functional categories</li> <li>Includes examples of code that can be cut and pasted into a design using a text editor</li> </ul>              |

| Virtex-4 Libraries Guide for<br>Schematic Designs            | <ul> <li>Includes a general description of the Virtex-4 LX/SX/FX architectures</li> <li>Includes a list of all of the Virtex-4 design elements for which schematic symbols are available, organized by their respective functional categories</li> </ul>                                                                                               |

| Title                                             | Summary                                                                                                                                                                                                                                                                                                                          |

|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Virtex-5 Libraries Guide for HDL Designs          | <ul> <li>Includes a general description of the Virtex-5 architectures</li> <li>Includes a list of all Virtex-5 design elements that can be instantiated using VHDL or Verilog code organized by functional categories</li> <li>Includes examples of code that can be cut and pasted into a design using a text editor</li> </ul> |

| Virtex-5 Libraries Guide for<br>Schematic Designs | <ul> <li>Includes a general description of the Virtex-5 architectures</li> <li>Includes a list of all of the Virtex-5 design elements for which schematic symbols are available, organized by their respective functional categories</li> </ul>                                                                                  |